《功能材料与器件学报》

摩尔定律会如何发展?纳米片器件发话了...

来源:功能材料与器件学报 【在线投稿】 栏目:综合新闻 时间:2021-08-09

现代微处理器是世界上最复杂的系统之一,但其核心是一个非常简单而优美的器件——晶体管。如今的微处理器中有数十亿个近乎完全相同的晶体管。因此,提高晶体管的性能和密度是促使微处理器及受其驱动的计算机更高效工作的最直接的方法。

这是摩尔定律的前提,即便现在它已经(几乎)走向了终点。制造更小、更好的微处理器晶体管愈发困难,而且昂贵无比。只有英特尔、三星和台积电(TSMC)具备在这一微型化前沿领域开展业务的能力。它们都在制造相当于7纳米节点的集成电路。这是摩尔定律初期遗留下来的名称,现已没有明确的实际意义,但它仍然反映了集成电路功能和器件微型化的程度。

目前7纳米制造工艺已属前沿技术,但三星和台积电今年4月宣布,他们将开始转向5纳米节点。三星还另外宣布,公司认为,行业使用了近10年的晶体管已经完成使命,新一代3纳米节点将在2020年前后开始限量生产,目前它正用于一项全新设计。

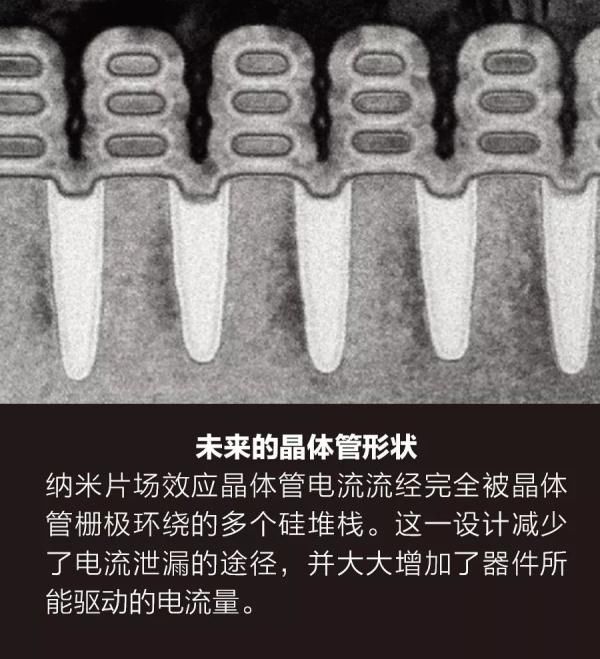

这类晶体管名称繁多,有环绕式栅极、多桥沟道、纳米梁等,但在研究领域,我们一直称它为纳米片。名称不是很重要,重要的是,它并非只是为逻辑芯片设计的下一代晶体管;它很可能是最后一代。当然,侧重的主题会有所变化,但从现在起可能全部都是纳米片。

金属氧化物半导体场效应晶体管(MOSFET,即微处理器中使用的晶体管)自1959年诞生以来,其形状和材料都发生了变化,但基本结构(栅极叠层、沟道区域、源极和漏极)一直保持不变。在其原始形式中,源极、漏极和沟道基本上是硅掺杂其他元素原子的区域,这样就可以形成一个移动负电荷丰度(n型)或一个移动正电荷丰度(p型)区域。我们需要两种类型的晶体管来实现构成当前计算机芯片的互补金属氧化物半导体(CMOS)技术。

MOSFET的栅极叠层位于沟道区域的正上方。当前的栅极叠层由介电材料层上的金属(用于栅极)制成。这种组合旨在使晶体管沟道区域形成电场,同时防止电荷泄漏。

向栅极施加足够大的电压(相对于源极),就会在电介质和硅之间的界面附近形成一层移动电荷载流子。电荷载流子完全桥接源极和漏极后,电流即可通过。将栅极电压降至接近于零,会关闭传导通路。

当然,要使电流从源极流向漏极,首先需要在沟道上设置电压。随着晶体管结构越来越小,这种电压带来的影响最终会导致晶体管历史上最大的形状变化。

这是因为源极-漏极电压可以在电极之间形成自身的导电区域。随着每一代晶体管诞生,沟道区域越来越短,漏极电压的影响也越来越大。电荷会泄漏到栅极附近区域下方,从而导致晶体管永远不会完全关闭,浪费电能并产生热量。

为了阻止多余的电荷流,沟道区域必须变薄,从而限制电荷通过的路径。栅极需要从多个侧面环绕沟道。因此,鳍式场效应晶体管(FinFET)应运而生。其沟道区域的两侧向上倾斜,在源极和漏极之间形成了一个细长的“硅鳍”,为电流流通提供了更宽的通道。之后栅极和电介质以三面而非一面覆盖在鳍上。

FinFET无疑取得了巨大成功。虽然FinFET在十多年前就已问世,但直到2011年,英特尔才率先推出了商业化的22纳米节点FinFET,三星、台积电等公司紧随其后。从那时起,在摩尔定律扩展的最后阶段,它始终是尖端硅逻辑的主力。可惜花无百日红。

FinFET无法向3纳米节点推进。十多年前,我们三人和其他人一样,以这样或那样的形式预见到了这一点。

尽管FinFET性能优越,但它自身也存在着问题。首先,它引入了一个原“平面”晶体管没有的设计缺陷。要认清这个问题,必须了解到,在晶体管的速度、功耗、制造复杂性和成本之间需要相互权衡。这种权衡与沟道宽度有很大关系,沟道宽度在器件设计领域称为Weff。宽度增大意味着可以驱动更多的电流,更快地开关晶体管,但这也会导致制造过程更复杂、成本更高。

在平面器件中,可以通过调整沟道的几何形状来进行平衡,但是FinFET鳍的灵活性欠佳。连接晶体管形成电路的金属互连线成层地排布在晶体管之上。正因如此,在不干扰互连层的情况下,晶体管鳍的高度(相当于平面设计中的宽度)不能发生太大变化。如今,芯片设计师通过制造具有多个鳍的单个晶体管来解决这一问题。

FinFET的另一个短板是,它的栅极仅三面环绕矩形硅鳍,使得底部与硅体相连,因而泄漏电流可以在晶体管关闭时流动。许多研究人员推断,要实现对沟道区域的终极控制,栅极需要完全将其环绕。